Custom Intelligent Hardware Lab

Chixiao Chen, Ph.D

Ass. Prof in Fudan University, PR China

Contact me by cxchen@fudan.edu.cn

Publication

The page is OBSOLETE now. Since 2025, Prof. Chen and Zhu will update their publication in their own website or Google Scholar page.

Please check Chixiao Chen (Google Scholar) and Haozhe Zhu (Google Scholar).

Chiplet Technology and Systems of Integrated Chips

- Y. Yang, Y. Wang, T. Yi, C. Chen, Q Liu, “A 6.4-Gbps 0.41-pJ/b fully-digital die-to-die interconnect PHY for silicon interposer based 2.5D integration”, Integration VLSI, Volume 96, 2024.

- C. Chen et al., “Design Challenges of Intrachiplet and Interchiplet Interconnection,” in IEEE Design & Test, vol. 39, no. 6, pp. 99-109, Dec. 2022

- J. Liao , …, C. Chen, “A Scalable Die-to-Die Interconnect with Replay and Repair Schemes for 2.5D/3D Integration,” ISCAS 2023.

In-memory Computing Macros and Chips

- H. Zhu, …, and C. Chen, “Trident-CIM: A LUT-Based Compute-in-Memory Macro With Trident Read Bit-Line and Partial Product Pruning,” in IEEE TCAS-II.(Early Access)

- S. Liu, …, C. Chen, “HARDSEA: Hybrid Analog-ReRAM Clustering and Digital-SRAM In-Memory Computing Accelerator for Dynamic Sparse Self-Attention in Transformer,” in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 32, no. 2, pp. 269-282, Feb. 2024. (Corresponding Author)

- S. Liu, …, C. Chen, Q. Liu, M. Liu, “A 28nm 53.8TOPS/W 8b Sparse Transformer Accelerator with In-Memory Butterfly Zero Skipper for Unstructured-Pruned NN and CIM-Based Local-Attention-Reusable Engine,” ISSCC 2023. (Corresponding Author)

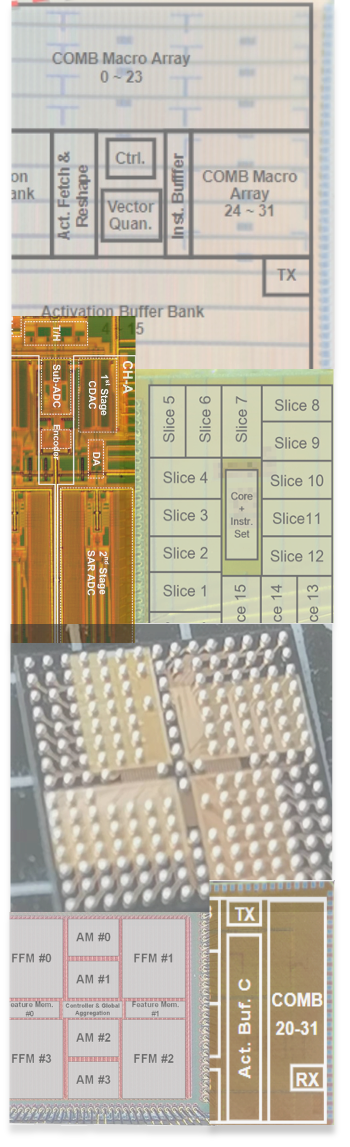

- H. Zhu, …, C. Chen, …, M. Liu, “COMB-MCM: Computing-on-Memory-Boundary NN Processor with Bipolar Bitwise Sparsity Optimization for Scalable Multi-Chiplet- Module Edge Machine Learning,” ISSCC 2022. (Corresponding Author)

- C. Mu …, C. Chen, Q. Liu, “A 200M-Query-Vector/s Computing-in-RRAM ADC-less k-Nearest-Neighbor Accelerator with Time-Domain Winner-Takes-All Circuits,” AICAS 2022, Incheon, Korea. (Corresponding Author)

- K. Zhou …, C. Chen, …, M. Liu, “A 28 nm 81 Kb 59–95.3 TOPS/W 4T2R ReRAM Computing-in-Memory Accelerator With Voltage-to-Time-to-Digital Based Output,” IEEE JETCAS, vol. 12, no. 4, pp. 846-857, Dec. 2022.

- S. Liu, H. Zhu, C. Chen, L. Zhang and C. -J. Richard Shi, “XNORAM: An Efficient Computing-in-Memory Architecture for Binary Convolutional Neural Networks with Flexible Dataflow Mapping,” 2020 2nd IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), Genova, Italy, 2020, pp. 21-25. (Corresponding Author)

- H. Zhu, C. Chen, et al., “A Communication-Aware DNN Accelerator on ImageNet Using in-Memory Entry-Counting Based Algorithm-Circuit-Architecture Co-Design in 65nm CMOS,” in IEEE Journal on Emerging and Selected Topics in Circuits and System. (Corresponding Author)

Deep Learning Processor

- J. Zheng, …, C. Chen and Q. Liu, “TiPU: A Spatial-Locality-Aware Near-Memory Tile Processing Unit for 3D Point Cloud Neural Network,” DAC 2023. (Corresponding Author)

- H. Jiang , …, C. Chen and Q. Liu, “A 2.53μW/channel Event-Driven Neural Spike Sorting Processor with Sparsity-Aware Computing-In-Memory Macros,” ISCAS 2023. (Corresponding Author)

- C. Chen, X. Liu, H. Peng, H. Ding and C. -. Richard Shi, “iFPNA: A Flexible and Efficient Deep Learning Processor in 28-nm CMOS Using a Domain-Specific Instruction Set and Reconfigurable Fabric,” in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 9, no. 2, pp. 346-357, June 2019.

- C. Chen, et al., “Exploring the Programmability for Deep Learning Processors: from Architecture to Tensorization,” 2018 55th ACM/ESDA/IEEE Design Automation Conference (DAC), San Francisco, CA, 2018, pp. 1-6.

- C. Chen, et al., “iFPNA: A Flexible and Efficient Deep Neural Network Accelerator with a Programmable Data Flow Engine in 28nm CMOS,” ESSCIRC 2018 - IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, 2018, pp. 170-173.

- C. Chen, et al., “OCEAN: An On-Chip Incremental-Learning Enhanced Artificial Neural Network Processor With Multiple Gated-Recurrent-Unit Accelerators,” in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 8, no. 3, pp. 519-530, Sept. 2018.

- C. Chen, et al., “OCEAN: An on-chip incremental-learning enhanced processor with gated recurrent neural network accelerators,” ESSCIRC 2017 - 43rd IEEE European Solid State Circuits Conference, Leuven, 2017, pp. 259-262.

Mixed Signal Circuit and System Design (for ADCs and Sensors)

- W. Jiang, Y. Zhu, C. Chen, et al., “A 14b 500 MS/s Single-Channel Pipelined-SAR ADC With Reference Ripple Mitigation Techniques and Adaptively Biased Floating Inverter Amplifier,” in IEEE Journal of Solid-State Circuits, vol. 58, no. 10, pp. 2709-2721, Oct. 2023

- D. Zhai …, C. Chen, “High-Speed and Time-Interleaved ADCs Using Additive-Neural-Network-Based Calibration for Nonlinear Amplitude and Phase Distortion,” IEEE TCAS-I, vol. 69, no. 12, pp. 4944-4957, Dec. 2022.

- T. Zhang, Y. Cao, S. Zhang, C. Chen, F. Ye and J. Ren, “Machine Learning Based Prior-Knowledge-Free Calibration for Split Pipelined-SAR ADCs with Open-Loop Amplifiers Achieving 93.7-dB SFDR”, ESSCIRC 2019, Krakow pp.189-192. (speaker, co-corresponding author)

- A. Wang, C. Chen, C. Liu and C. R. Shi, “A 9-bit Resistor-Based Highly-Digital Temperature Sensor with a SAR-Quantization Embedded Differential Low-Pass Filter in 65nm CMOS with a 2.5μs Conversion Time,” in IEEE Sensors Journal.

- A. Wang, C. Chen and C. R. Shi, “A 9-bit Resistor-Based All-Digital Temperature Sensor with a SAR-Quantization Embedded Differential Low-Pass Filter in 65nm CMOS Consuming 57pJ with a 2.5 $\mu$s Conversion Time”, ICC 2019, Austin TX, April 2019.

- A. Wang, C. Chen and C. R. Shi, “Design and Analysis of an Always-ON Input-Biased pA-Current Sub-nW mV-Threshold Hysteretic Comparator for Near-Zero Energy Sensing,” in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 9, pp. 2284-2294, Sept. 2017.

- C. Chen, et al., “An ARMA-Model-Based NTF Estimation on Continuous-Time$\Delta\Sigma$Modulators,” in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 62, no. 8, pp. 721-725, Aug. 2015.

- C. Chen, et al., “A low-offset calibration-free comparator with a mismatch-suppressed dynamic preamplifier,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, 2014, pp. 2361-2364.

- C. Chen, et al., “An 8-bit 100-MS/s Digital-to-Skew Converter with 200-ps range for time-interleaved sampling,” 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, 2012, pp. 1100-1103.

- B. Yu, C. Chen, et al., “A 14-bit 200-MS/s time-interleaved ADC with sample-time error detection and cancelation,” IEEE Asian Solid-State Circuits Conference 2011, Jeju, 2011, pp. 349-352.