Custom Intelligent Hardware Lab

Chixiao Chen, Ph.D

Ass. Prof in Fudan University, PR China

Contact me by cxchen@fudan.edu.cn

Chixiao Chen 陈迟晓

Brief Introduction 简要介绍

复旦大学集成电路与微纳电子创新学院副研究员/博导,全国重点实验室集成芯片创新中心主任,绍芯实验室(复旦—绍芯研究院)副主任、国家自然科学基金委优青,上海市青年科技启明星。研究方向包括智能计算芯片与系统、面向先进封装/三维集成/芯粒技术的电路—封装—架构协同设计。任A-SSCC技术委员会委员,ICAC大会共主席、集成芯片与芯粒大会论坛组织主席等,获上海市技术进步一等奖。

Education & Experience 教育与工作经历

Fudan University 复旦大学 ~ Shanghai 上海, China

- B.Sc. in Department of Micro-electronics ~ 09/2006 - 07/2010

Fudan University 复旦大学 ~ Shanghai 上海, China

- Ph.D. in School of Micro-electronics ~ 09/2010 - 01/2016

University of Washington 美国华盛顿大学 ~ Seattle 西雅图, WA, USA

- Postdoc/Research Associate (博士后研究员) in EE Department ~ 08/2016 - 11/2018

Fudan Univeristy 复旦大学 ~ Shanghai 上海, China

-

Assistant Prof. (青年副研究员) in FICS (芯片与系统前沿技术研究院) ~ 12/2018 - 12/2021

-

Associate Prof. (副研究员) in ICNME (集成电路与微纳电子创新学院) & FICS ~ 01/2022 - Now

-

Director of Innoviation Center (创新中心主任) in SKL-ICS (集成芯片与系统全国重点实验室) ~ 09/2022 - Now

Shaoxin Laboratory 绍芯实验室 (复旦—绍兴研究院) ~ Shaoxing 绍兴, Zhejiang 浙江, China

- Vice Director (副主任) & Chief Scientist(存算一体首席科学家) ~ 09/2024 - Now

Selected Publications 代表性工作

-

[IEEE JSSC 2025] C. Mu, …, C. Chen, , “A 28nm RRAM/SRAM Collaborative CIM Accelerator Supporting RRAM-Endurance-LatencyAwareness for Edge Fine-Tuning”. (Corresponding Author 通讯作者)

-

[DAC 2025] S. Liu, …, C. Chen, “McPAL: Scaling Unstructured Sparse Inference with Multi-Chiplet HBM-PIM Architecture for LLMs”. (Corresponding Author 通讯作者)

-

[IEEE JSSC 2025] S. He , …, C. Chen, et al. “A 22-nm 109.3-to-249.5-TFLOPS/W Outlier-Aware Floating-Point SRAM Compute-in-Memory Macro for Large Language Models”. (Corresponding Author 通讯作者)

-

[HPCA 2025] S. Jia, … , C. Chen, Q. Liu, M. Liu, “EIGEN: Enabling Efficient 3DIC Interconnect with Heterogeneous Dual-Layer Network-on-Active-Interposer”. (Corresponding Author 通讯作者, 体系结构顶会)

-

[ISSCC 2025] B. Jiao, … , C. Chen, Q. Liu, M. Liu, “SHINSAI: A 586mm2 Reusable Active TSV Interposer with Programmable Interconnect Fabric and 512Mb 3D Underdeck Memory”. (Corresponding Author 通讯作者)

-

[IEEE TCAS-I 2024] B. Jiao … , C. Chen, et al., “FPIA: Communication-Aware Multi-Chiplet Integration With Field-Programmable Interconnect Fabric on Reusable Silicon Interposer”. (Corresponding Author 通讯作者)

-

[IEEE JSSC 2024] M. Li, …, C. Chen, et al., “SLAM-CIM: A Visual SLAM Backend Processor With Dynamic-Range-Driven-Skipping Linear-Solving FP-CIM Macros”. (Corresponding Author 通讯作者)

-

[ISSCC 2023] S. Liu, , …, C. Chen, Q. Liu, M. Liu, “A 28nm 53.8TOPS/W 8b Sparse Transformer Accelerator with In-Memory Butterfly Zero Skipper for Unstructured-Pruned NN and CIM-Based Local-Attention-Reusable Engine”. (Corresponding Author 通讯作者)

-

[ISCAS 2023] J. Liao, …, C. Chen, “A Scalable Die-to-Die Interconnect with Replay and Repair Schemes for 2.5D/3D Integration”. (Corresponding Author 通讯作者)

-

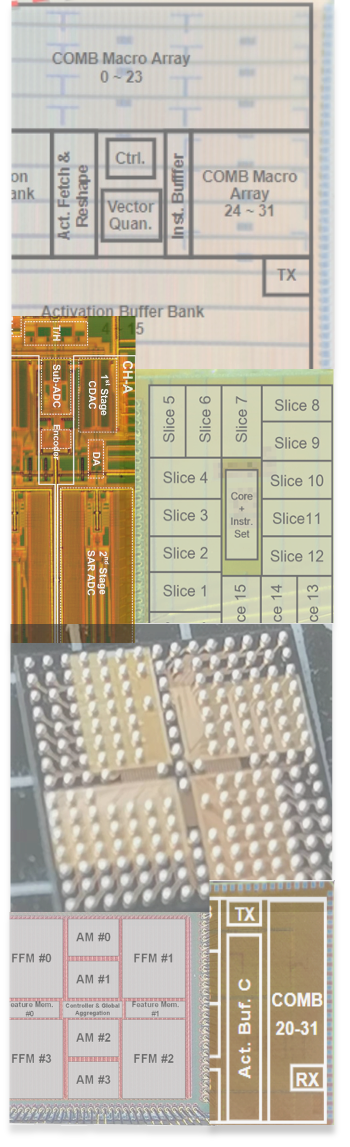

[ISSCC 2022] H. Zhu, …, C. Chen, et al, “COMB-MCM: Computing-on-Memory-Boundary NN Processor with Bipolar Bitwise Sparsity Optimization for Scalable Multi-Chiplet-Module Edge Machine Learning”. (Corresponding Author 通讯作者)

-

[IEEE D&T 2022] C. Chen, et al., “Design Challenges of Intra-chiplet and Inter-chiplet Interconnection”. (First Author 第一作者)

Awards and Honors 奖励情况

上海市技术发明一等奖 (2022)

中国光学工程学会科技进步一等奖 (2024)

A-SSCC Distinguished Design Award (2024)

IEEE Solid State Circuits Society Outstanding Reviewer (2023, 2024)

复旦大学青年五四奖章(集体) (2025,获奖主体为CiHLab)